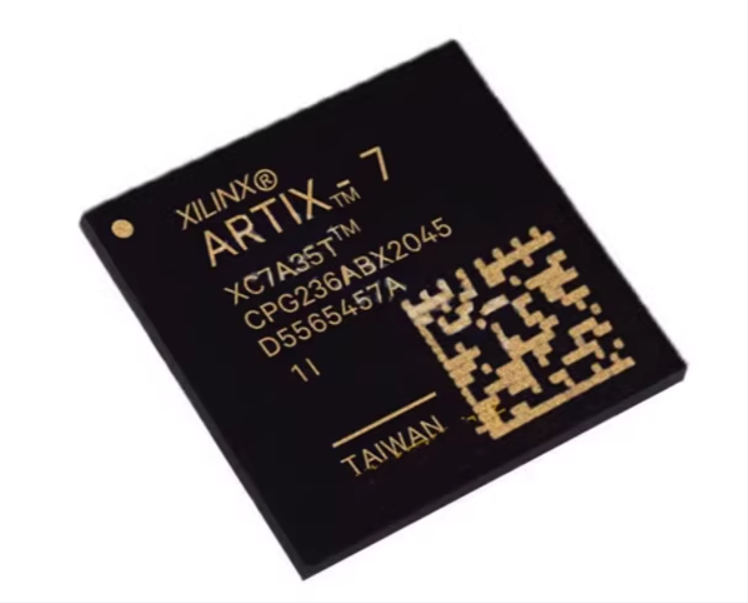

Dekodowanie numeru części

| Pole | Znaczenie |

|---|---|

| EP | Prefiks rodziny układów FPGA firmy Intel (Altera) |

| 3S | Stratix III generacji, proces 65 nm |

| L50 | Wariant zoptymalizowany pod kątem logiki, ≈47,5 k LE |

| F780 | 780-pinowy układ FineLine BGA, odstęp 1,0 mm |

| I | Temperatura przemysłowa -40 °C do 100 °C |

| 3 | Najszybsza komercyjna klasa prędkości (-3) |

Podstawowe specyfikacje

| Parametr | Wartość | Uwagi |

|---|---|---|

| Elementy logiczne | 47 500 LE | ≈19 000 ALM, 4-wejściowe LUT |

| Pamięć wbudowana | 2,08 Mbit | Bloki M9K, z obsługą ECC |

| Bloki DSP | 92 × 18×18 | Możliwość kaskadowania do 36×36 |

| PLL | 8 | Fractional-N, dynamiczne przesunięcie fazowe |

| We/Wy użytkownika | 488 maks | 24 banki, wiele standardów |

| Napięcie rdzenia | 1,1 V ± 3 % | Banki wejść/wyjść 2,5 V / 3,3 V |

| Redukcja mocy | ≈50 % statyczny | Bramkowanie mocy na blok |

Najważniejsze informacje o architekturze

- Tkanina ALUT: Każdy adaptacyjny moduł logiczny (ALM) zawiera 4-wejściową LUT plus dwa sumatory, umożliwiając 6-wejściowe funkcje lub podwójne 4-wejściowe funkcje, poprawiając wykorzystanie o ≈20 % w porównaniu do stałych projektów LUT-4.

- Kolumna DSP: Bloki Half-DSP działają z częstotliwością 550 MHz w trybach 18-bitowym, 36-bitowym lub 54-bitowym; łańcuchy kaskadowe obsługują filtry FIR > 256 odczepów bez routingu tkaniny.

- Zegar: Globalne, regionalne i peryferyjne sieci zapewniają wydajność do 550 MHz; dynamiczny krok fazowy dla łączy źródłowo-synchronicznych.

- Banki we/wy: Osiem banków z niezależnymi

VCCIOi automatyczna kalibracja zakończeń na chipie (OCT); grupy DQS obsługują DDR3-800.

Wytyczne dotyczące projektowania PCB i zasilania

- Pakiet: 29 mm × 29 mm FineLine BGA, skok 1,0 mm; zalecana płytka 8-warstwowa z przelotkami, aby pominąć wszystkie 488 kulek użytkownika.

- Odsprzęganie: 0,1 µF X7R na pin zasilania plus 10 µF luzem; docelowa impedancja 10 mΩ przy 100 MHz.

- Sekwencjonowanie: Rdzeń 1,1 V przed 2,5 V aux; 50 ms miękkiego startu w celu uniknięcia zaniku napięcia. Moduły Intel Enpirion 10 A są zatwierdzonymi towarzyszami.

- Termiczny: θJA ≈ 11 °C/W nieruchomego powietrza; przepływ powietrza 200 LFM lub radiator 25 mm powyżej 70 °C otoczenia.

Przepływ narzędzi i weryfikacja

- Quartus II 9.0+ / Prime Lite: Włączenie opcji "Power-Driven Compilation" i "Physical Synthesis for Performance", aby przekroczyć 200 MHz w projektach wymagających dużej mocy obliczeniowej DSP.

- SignalTap II: Głębokość próbkowania 2 kB przy 250 MHz wystarcza do większości debugowania maszyn stanów.

- ModelSim-Altera 6.6b+: Wstępnie skompilowane biblioteki Stratix III skracają czas konfiguracji do <2 min.

- JTAG: Plik BSDL obsługuje IEEE 1532 ISP i aktualizacje oprogramowania układowego w czasie rzeczywistym.

Typowe zastosowania

| Domena | Przypadek użycia | Dźwignia funkcji |

|---|---|---|

| Wizja maszynowa | Wykrywanie krawędzi 1080p60 | 92 bloki DSP + wejścia/wyjścia LVDS |

| SDR Baseband | 2×2 MIMO DUC/DDC | MAC 550 MHz + deterministyczny PLL |

| Ruch przemysłowy | 8-osiowa pętla serwo | 488 wejść/wyjść + temp. przemysłowa |

| Karta kanałów ATE | Generator wzorców | SSTL-15, OCT |

Migawka między dostawcami

| Sprzedawca | Urządzenie | Logika (kLE) | DSP (18×18) | SerDes (Gb/s) | Węzeł (nm) |

|---|---|---|---|---|---|

| Intel | EP3SL50F780I3 | 47.5 | 92 | - | 65 |

| Intel | 10AX027H2F34I2SG | 27 | 96 | 17.4 | 20 |

| Xilinx | XC7K70T-2FBG676I | 65 | 240 | 12.5 | 28 |

Wybierz EP3SL50, gdy starsze łańcuchy dostaw 65 nm i sprawdzona niezawodność klasy przemysłowej przeważają nad potrzebą szybkich transceiverów.

Pułapki i łagodzenie skutków

- Czas zamknięcia: Włącz "Perform Register Duplication" dla częstotliwości > 300 MHz.

- Konfiguracja Flash: Użyj EPCQ16A lub większego; EPCS nie posiada kompresji strumienia bitów.

- Hot-Socket: Ograniczenie I/O do maks. 3,6 V podczas wstawiania.

Zamówienia publiczne

W celu uzyskania natychmiastowych próbek lub zamówień hurtowych można skontaktować się z dostawcą za pośrednictwem poniższego e-maila kontaktowego..

Uzyskaj najlepszą cenę od EQGOO!

10 tysięcy modeli w magazynie! Czekamy tylko na Twoje zapytanie!