Przegląd i analiza architektury

The XCZU5CG-1SFVC784I to wysokowydajny System-on-Chip (SoC) od Xilinx Zynq UltraScale+ MPSoC rodzina, w tym:

Zalety architektury heterogenicznej

XCZU5CG architektura heterogeniczna umożliwia wyspecjalizowaną dystrybucję zadań w celu uzyskania optymalnej wydajności w aplikacjach przemysłowych i AI:

Klaster Cortex-A53

Obsługuje wysokopoziomowy system operacyjny (Linux) i złożone algorytmy, takie jak planowanie ścieżki i rozpoznawanie obrazu, dzięki czterordzeniowej mocy obliczeniowej.

Rdzenie Cortex-R5

Zapewnia deterministyczną reakcję w czasie rzeczywistym (poziom μs) dla sterowania ruchem i operacji krytycznych dla bezpieczeństwa z dwurdzeniową redundancją.

Programowalny układ logiczny

Implementuje niestandardowe akceleratory sprzętowe do wstępnego przetwarzania obrazu, akceleracji protokołów (EtherCAT/PROFINET) i wnioskowania AI.

Aplikacje automatyki przemysłowej

Inteligentna platforma kontroli produkcji

Odpowiedź na poziomie milisekund dla wieloosiowych systemów sterowania ruchem:

- A53 obsługuje algorytmy planowania ścieżki

- R5 zarządza pętlami sterowania serwomechanizmami w czasie rzeczywistym

- PL przyspiesza protokoły przemysłowe (EtherCAT/PROFINET)

Przemysłowe systemy kontroli wizyjnej

Zastępuje tradycyjne przemysłowe rozwiązania PC + karta przechwytująca:

- Zaimplementowany w PL potok wstępnego przetwarzania obrazu (filtrowanie, wykrywanie krawędzi)

- Algorytmy rozpoznawania defektów oparte na A53

- 70% redukcja rozmiaru systemu i zużycia energii

Przemysłowe bramy IoT

Bogata obsługa interfejsu dla różnorodnych połączeń:

- Podwójny Gigabit Ethernet (autonegocjacja 10/100/1000 Mb/s)

- USB 3.0 (przepustowość do 5 Gb/s)

- Magistrala CAN FD (do 5 Mb/s)

- Interfejsy przemysłowe RS232/RS485

Możliwości AI Edge Computing

XCZU5CG umożliwia Wnioskowanie o sztucznej inteligencji na urządzeniu z:

- Wdrożenie DPU Xilinx w PL dla akceleracji CNN (do 5 TOPS)

- Obsługa ram poprzez Vitis AI toolchain:

- TensorFlow Lite

- Modele kwantyzowane PyTorch

- Typowe zastosowania:

- Inteligentne rozpoznawanie twarzy/wad aparatu

- SLAM i nawigacja wizualna robota mobilnego

- Przetwarzanie sygnałów urządzeń medycznych (USG, CT)

Wsparcie rozwoju i ekosystem

Oficjalny zestaw narzędzi Xilinx

- Vivado Design Suite - Projektowanie sprzętu i konfiguracja PL

- Zunifikowana platforma oprogramowania Vitis - Tworzenie aplikacji heterogenicznych

- Vitis AI - Optymalizacja i wdrażanie modeli AI

- Narzędzia PetaLinux - Rozwój wbudowanego systemu Linux

- Xilinx Runtime (XRT) - Czas działania akceleracji FPGA

- Vitis HLS - Synteza wysokiego poziomu dla akceleracji algorytmów

- Środowisko programistyczne SDSoC - Projektowanie na poziomie systemu

Wsparcie osób trzecich

- Płyty rozwojowe firm Zhen Dian Zi, Enclustra i Avnet

- Wsparcie open-source (Yocto Project, Buildroot)

- Stosy protokołów przemysłowych (OPC UA, Modbus, DDS)

- Rozwiązania middleware (ROS 2, AUTOSAR)

Podsumowanie podstawowych zalet

Wydajność w czasie rzeczywistym

Podwójne rdzenie R5 zapewniają reakcję na poziomie μs dla zadań sterowania przemysłowego z determinizmem na poziomie sprzętowym.

Elastyczne przyspieszenie

PL obsługuje niestandardowe akceleratory sprzętowe poprzez implementację Vitis HLS lub RTL.

Wysoka integracja

Rozwiązanie jednoukładowe integruje system przetwarzania, jednostkę czasu rzeczywistego i programowalny układ logiczny.

Bogate interfejsy

Obsługuje ponad 15 przemysłowych standardów komunikacyjnych i szybkich interfejsów danych.

Dostęp do dokumentacji technicznej

Kompletna dokumentacja techniczna jest niezbędna do zaprojektowania systemu:

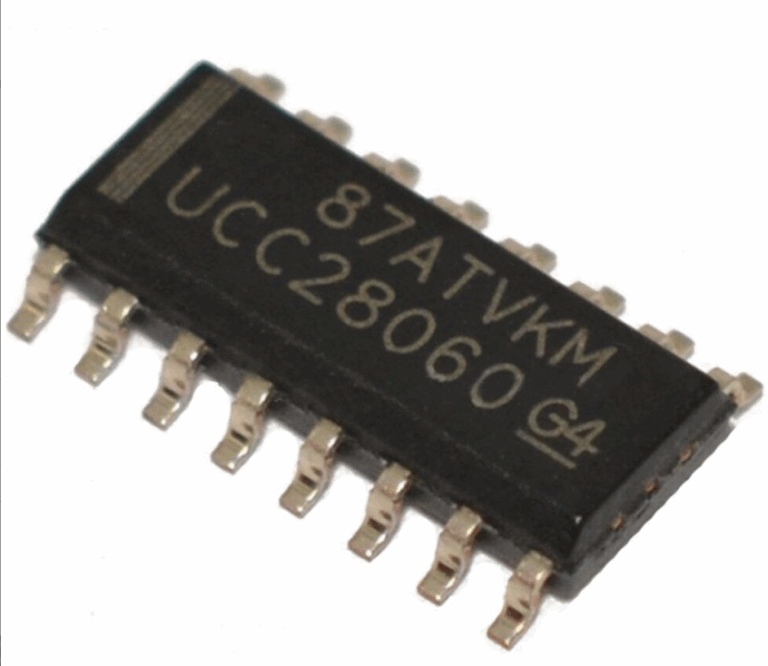

- Karta katalogowa (DS890) - Charakterystyka elektryczna i wyprowadzenia

- Instrukcja techniczna (UG1085) - Szczegóły architektury

- Przewodnik projektowania PCB (UG933) - Zalecenia dotyczące układu

- Arkusz kalkulacyjny szacowania mocy - Obliczenia termiczne

Dostępne od Oficjalna strona internetowa AMD Xilinx po rejestracji.

Uzyskaj najlepszą cenę od EQGOO!

10 tysięcy modeli w magazynie! Czekamy tylko na Twoje zapytanie!