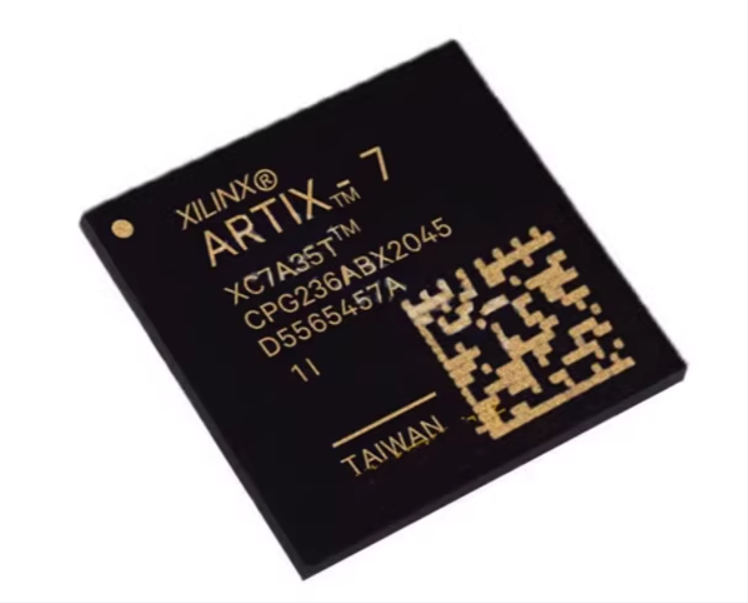

Penguraian Nomor Bagian

| Bidang | Arti |

|---|---|

| EP | Awalan keluarga FPGA Intel (Altera) |

| 3S | Generasi Stratix III, proses 65 nm |

| L50 | Varian yang dioptimalkan secara logika, ≈47,5 k LE |

| F780 | BGA FineLine 780-pin, pitch 1,0 mm |

| I | Suhu industri -40 °C hingga 100 °C |

| 3 | Tingkat kecepatan komersial tercepat (-3) |

Spesifikasi Inti

| Parameter | Nilai | Keterangan |

|---|---|---|

| Elemen Logika | 47 500 LE | ≈19.000 ALM, LUT 4 masukan |

| Memori Tertanam | 2,08 Mbit | Blok M9K, berkemampuan ECC |

| Blok DSP | 92 × 18×18 | Dapat di-cascade hingga 36×36 |

| PLL | 8 | Pecahan-N, pergeseran fase dinamis |

| I / O Pengguna | 488 maks | 24 bank, multi-standar |

| Tegangan Inti | 1,1 V ± 3 % | Bank I/O 2,5 V / 3,3 V |

| Pengurangan Daya | ≈50 % statis | Gerbang daya per blok |

Sorotan Arsitektur

- Kain ALUT: Setiap modul logika adaptif (ALM) berisi LUT 4 masukan ditambah dua adder, memungkinkan fungsi 6 masukan atau fungsi 4 masukan ganda, meningkatkan pemanfaatan sebesar ≈20 % dibandingkan desain LUT-4 yang tetap.

- Kolom DSP: Blok Half-DSP beroperasi pada 550 MHz dalam mode 18-bit, 36-bit, atau 54-bit; rantai kaskade mendukung filter FIR > 256 tap tanpa perutean kain.

- Jam: Jaringan global, regional, dan periferal menghadirkan performa fabric hingga 550 MHz; loncatan fase dinamis untuk tautan sinkronisasi sumber.

- Bank I/O: Delapan bank dengan status independen

V CCIOdan kalibrasi otomatis penghentian on-chip (OCT); kelompok DQS mempertahankan DDR3-800.

Panduan Desain PCB & Daya

- Paket: BGA FineLine 29 mm x 29 mm, pitch 1,0 mm; papan 8 lapis dengan via-in-pad yang direkomendasikan untuk meloloskan 488 bola pengguna.

- Decoupling: 0,1 µF X7R per pin daya ditambah 10 µF curah; target impedansi 10 mΩ pada 100 MHz.

- Pengurutan: Core 1.1 V sebelum aux 2.5 V; soft-start 50 ms untuk menghindari brownout. Modul Intel Enpirion 10 A adalah pendamping yang tervalidasi.

- Panas: θJA ≈ 11 °C/W udara diam; aliran udara 200 LFM atau heatsink 25 mm di atas suhu 70 °C.

Alur & Verifikasi Alat

- Quartus II 9.0+ / Prime Lite: Aktifkan "Kompilasi Berbasis Daya" dan "Sintesis Fisik untuk Performa" untuk melampaui 200 MHz pada desain DSP-berat.

- SignalTap II: Kedalaman sampel 2 kB @ 250 MHz cukup untuk sebagian besar debug mesin negara.

- ModelSim-Altera 6.6b+: Pustaka Stratix III yang sudah dikompilasi sebelumnya memangkas waktu penyiapan hingga < 2 menit.

- JTAG: File BSDL mendukung IEEE 1532 ISP dan pembaruan firmware waktu nyata.

Aplikasi Khas

| Domain | Kasus Penggunaan | Fitur Leveraged |

|---|---|---|

| Visi Mesin | Deteksi tepi 1080p60 | 92 blok DSP + I / O LVDS |

| SDR Baseband | 2 × 2 MIMO DUC / DDC | MAC 550 MHz + PLL deterministik |

| Gerakan Industri | Lingkaran servo 8 sumbu | 488 I/O + suhu industri |

| Kartu Saluran ATE | Generator pola | SSTL-15, OKTOBER |

Cuplikan Lintas Vendor

| Vendor | Perangkat | Logika (kLE) | DSP (18×18) | SerDes (Gbps) | Simpul (nm) |

|---|---|---|---|---|---|

| Intel | EP3SL50F780I3 | 47.5 | 92 | - | 65 |

| Intel | 10AX027H2F34I2SG | 27 | 96 | 17.4 | 20 |

| Bahasa Indonesia: Xilinx | XC7K70T-2FBG676I | 65 | 240 | 12.5 | 28 |

Pilih EP3SL50 ketika rantai pasokan 65 nm yang sudah ada dan keandalan tingkat industri yang telah terbukti lebih penting daripada kebutuhan akan transceiver berkecepatan tinggi.

Perangkap & Mitigasi

- Penutupan Waktu: Aktifkan "Lakukan Duplikasi Register" untuk > 300 MHz.

- Config Flash: Gunakan EPCQ16A atau yang lebih besar; EPCS tidak memiliki kompresi bitstream.

- Soket Panas: Batasi I/O hingga 3,6 V maks selama penyisipan.

Pengadaan

Untuk sampel langsung atau pesanan massal, Anda dapat menghubungi pemasok melalui email kontak di bawah ini..

Dapatkan Harga Terbaik Dari EQGOO!

Tersedia 10 ribu model! Menunggu pertanyaan Anda!