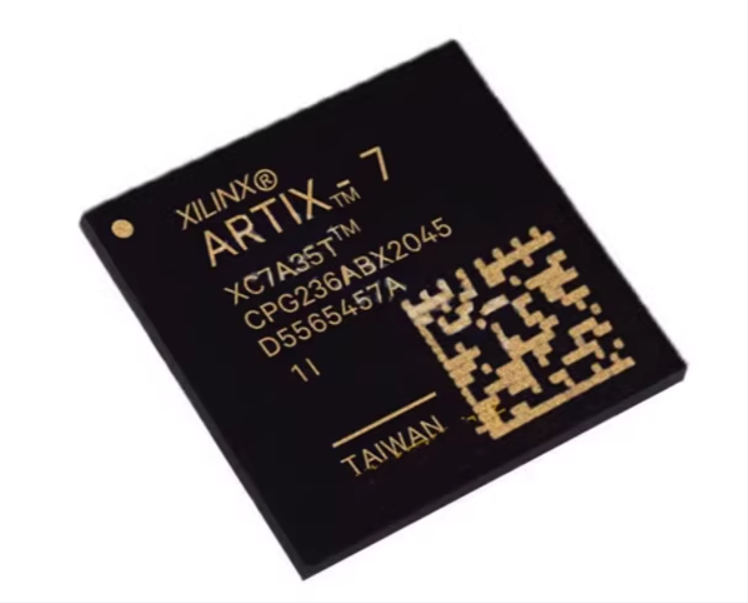

Part Number Decoding

| Field | Meaning |

|---|---|

| EP | Intel (Altera) FPGA family prefix |

| 3S | Stratix III generation, 65 nm process |

| L50 | Logic-optimized variant, ≈47.5 k LE |

| F780 | 780-pin FineLine BGA, 1.0 mm pitch |

| I | Industrial temperature –40 °C to 100 °C |

| 3 | Fastest commercial speed grade (-3) |

Core Specifications

| Parameter | Value | Remarks |

|---|---|---|

| Logic Elements | 47 500 LE | ≈19 000 ALMs, 4-input LUTs |

| Embedded Memory | 2.08 Mbit | M9K blocks, ECC capable |

| DSP Blocks | 92 × 18×18 | Cascadable up to 36×36 |

| PLLs | 8 | Fractional-N, dynamic phase shift |

| User I/O | 488 max | 24 banks, multi-standard |

| Core Voltage | 1.1 V ± 3 % | 2.5 V / 3.3 V I/O banks |

| Power Reduction | ≈50 % static | Per-block power gating |

Architecture Highlights

- ALUT Fabric: Each adaptive logic module (ALM) contains a 4-input LUT plus two adders, enabling 6-input functions or dual 4-input functions, improving utilization by ≈20 % over fixed LUT-4 designs.

- DSP Column: Half-DSP blocks operate at 550 MHz in 18-bit, 36-bit, or 54-bit modes; cascade chains support FIR filters > 256 taps without fabric routing.

- Clocking: Global, regional, and peripheral networks deliver up to 550 MHz fabric performance; dynamic phase stepping for source-synchronous links.

- I/O Banks: Eight banks with independent

VCCIOand on-chip termination (OCT) auto-calibration; DQS groups sustain DDR3-800.

PCB & Power Design Guidelines

- Package: 29 mm × 29 mm FineLine BGA, 1.0 mm pitch; 8-layer board with via-in-pad recommended to escape all 488 user balls.

- Decoupling: 0.1 µF X7R per power pin plus 10 µF bulk; target 10 mΩ impedance at 100 MHz.

- Sequencing: Core 1.1 V before 2.5 V aux; 50 ms soft-start to avoid brownout. Intel Enpirion 10 A modules are validated companions.

- Thermal: θJA ≈ 11 °C/W still air; 200 LFM airflow or 25 mm heatsink above 70 °C ambient.

Tool Flow & Verification

- Quartus II 9.0+ / Prime Lite: Enable “Power-Driven Compilation” and “Physical Synthesis for Performance” to exceed 200 MHz on DSP-heavy designs.

- SignalTap II: 2 kB sample depth @ 250 MHz suffices for most state-machine debug.

- ModelSim-Altera 6.6b+: Pre-compiled Stratix III libraries cut setup time to < 2 min.

- JTAG: BSDL file supports IEEE 1532 ISP and real-time firmware updates.

Typical Applications

| Domain | Use-Case | Feature Leveraged |

|---|---|---|

| Machine Vision | 1080p60 edge detection | 92 DSP blocks + LVDS I/O |

| SDR Baseband | 2×2 MIMO DUC/DDC | 550 MHz MACs + deterministic PLL |

| Industrial Motion | 8-axis servo loop | 488 I/O + industrial temp |

| ATE Channel Card | Pattern generator | SSTL-15, OCT |

Cross-Vendor Snapshot

| Vendor | Device | Logic (kLE) | DSP (18×18) | SerDes (Gbps) | Node (nm) |

|---|---|---|---|---|---|

| Intel | EP3SL50F780I3 | 47.5 | 92 | — | 65 |

| Intel | 10AX027H2F34I2SG | 27 | 96 | 17.4 | 20 |

| زیلینکس | XC7K70T-2FBG676I | 65 | 240 | 12.5 | 28 |

Choose EP3SL50 when legacy 65 nm supply chains and proven industrial-grade reliability outweigh the need for high-speed transceivers.

Pitfalls & Mitigation

- Timing Closure: Enable “Perform Register Duplication” for > 300 MHz.

- Config Flash: Use EPCQ16A or larger; EPCS lacks bitstream compression.

- Hot-Socket: Limit I/O to 3.6 V max during insertion.

Procurement

For immediate samples or bulk orders, you can contact the supplier via the contact email below..

بهترین قیمت را از EQGOO دریافت کنید!

10000 مدل موجود در انبار! فقط منتظر درخواست شما هستیم!